Characteristics of Modern Microprocessors

- Multicore processors: Modern processors can have between 2 (LCC- Low core count) to 24 (HCC – high core count) number of cores for parallelism at hardware level.

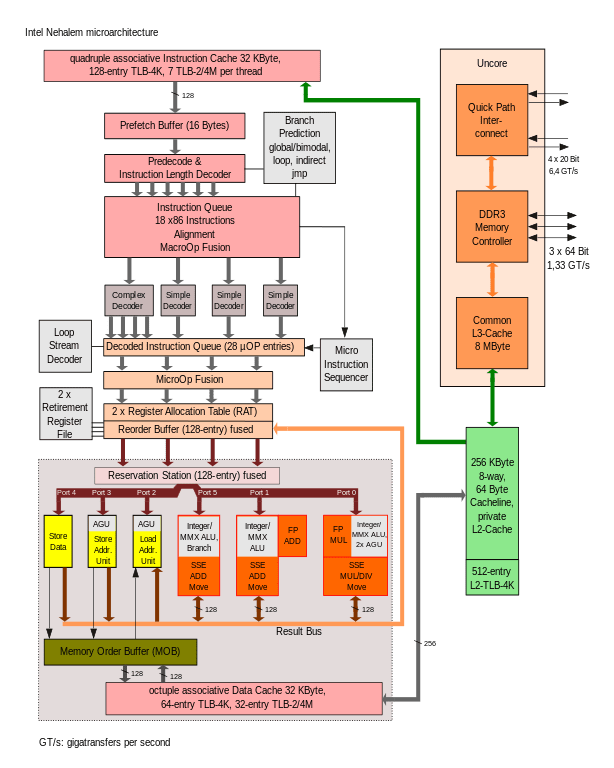

- out-of-order execution:

- In order to hide the ever widing gap between the CPU and main memory, all modern CPUs are pipelined and have execution reordering.

- While CPU is waiting for some data or instructions from memory, it might work on something else. There is a complex logic designed in hardware to check the input dependencies between instructions.

- Multi-level caches: There are atleast 3 levels of caches built in the processor which acts like local memory to the CPU.

- Speculative execution: Modern CPUs predict the memory location of data to next instruction that may be executed.

- Microops: The assembly instructions are divided into micro operations which makes it easy for execution and the result is then combined into one.

- Register renaming: The compilers can compile the code with logical registers like EAX, EBX, EDX etc. The processors have a lot of temporary registers. So it renames one of its temporary registers with logical names.

Architecture diagram for Intel Nehalem Processor

Image credit: By Appaloosa (Own work) [GFDL (http://www.gnu.org/copyleft/fdl.html) or CC-BY-SA-3.0 (http://creativecommons.org/licenses/by-sa/3.0/)%5D, via Wikimedia Commons

CPU Package Overview

Image credit: http://pages.rubrik.com/rs/794-OHF-673/images/vSphere_6.5_Host_Resources_Deep_Dive.pdf

Intel Xeon Uncore Elements

|

UNCORE ELEMENT |

DESCRIPTION |

RESPONSIBLE FOR |

|

QPI Agent |

Quick Path Interconnect |

QPI caching agent, manages R3QPI and QPI Link Interface. |

|

PCU |

Power Controller |

Core/Uncore power unit and thermal manager, governs P-State of the CPU, C-State of the Core and package. It enables Turbo Mode and can throttle cores when a thermal violation occurs. |

|

Ubox |

System Config Controller |

Intermediary for interrupt traffic between system and core. |

|

IIO |

Integrated IO |

Provides the interface to PCIe Devices. |

|

R2PCI |

Ring to PCI Interface |

Provides interface to the ring for PCIe access. |

|

IMC |

Integrated Memory Controller |

Provides the interface to RAM and communicates with Uncore through Home Agent. |

|

HA |

Home Agent |

Responsible for ordering read/writes coming from Ring to IMC. Provides directory cache coherency. |

|

SMI |

Scalable Memory Interface |

Provides IMC access to DIMMs. |

High Core Count Architecture

Image Credit: http://pages.rubrik.com/rs/794-OHF-673/images/vSphere_6.5_Host_Resources_Deep_Dive.pdf

Intel Xeon Processor Overview

|

GENERATION |

BRANDING |

YEAR |

PROCESS |

CADENCE |

MAX CORES |

|

Nehalem |

X5500 |

2008 |

45nm |

4 |

|

|

Westmere |

X5600 |

2010 |

32nm |

Tick |

6 |

|

Sandy Bridge |

E5-2600-v1 |

2012 |

32nm |

Tock |

8 |

|

Ivy Bridge |

E5-2600-v2 |

2013 |

22nm |

Tick |

12 |

|

Haswell |

E5-2600-v3 |

2014 |

22nm |

Tock |

18 |

|

Broadwell |

E5-2600-v4 |

2016 |

14nm |

Tick-Progress |

22 |

|

Skylake |

2P |

2017 |

14nm |

Architecture |

28 |

Image Credit: http://pages.rubrik.com/rs/794-OHF-673/images/vSphere_6.5_Host_Resources_Deep_Dive.pdf